前言

这是我以前在学校做编译原理实验时做的笔记,遇到不少的坑,但是最后还是完成了。这是一篇搭建SpinalHDL的教学,希望对读者有帮助。做完这个实验后我好兴幸自己不是读硬件有关的专业而是读软件

对硬件设计有点了解读者都知道Verilog吧,写小项目的时候觉得还好,但是写大项目的时候,只要想改一点点东西,就要改成千上万行代码,工作量巨大。所以,基于Scala的SpinalHDL框架就出来了,成功解决了上述问题。在添加标签时没有SpinalHDL标签,又不能创建,这知名度也太低了吧

工欲善其事,必先利其器 -- 《论语·卫灵公》

环境安装前置预备

IDEA安装

从官网下载,选Community版,完成后需安装Scala插作(先装IDEA然后往下做,等下再装插件)。

官网:https://www.jetbrains.com/idea/download/#section=windows

JDK安装

SpinalHDl基于Scala,Scala基于Java,下载Java SDK 1.8,从官网下载,选Java SE 8

官网:https://www.oracle.com/java/technologies/javase-downloads.html

详细安装JDK:https://www.liaoxuefeng.com/wiki/1252599548343744/1280507291631649

Scala与SBT安装

官网:https://www.scala-lang.org/

建议安装Scala 2.11.12版本

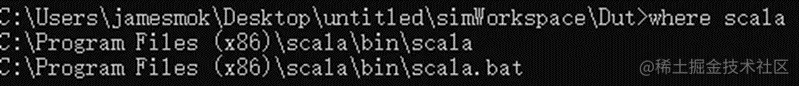

安装后,打开cmd,输入where Scala指令查看Scala安装路径

增加环境变量 Path: C:\Program Files (x86)\scala\bin

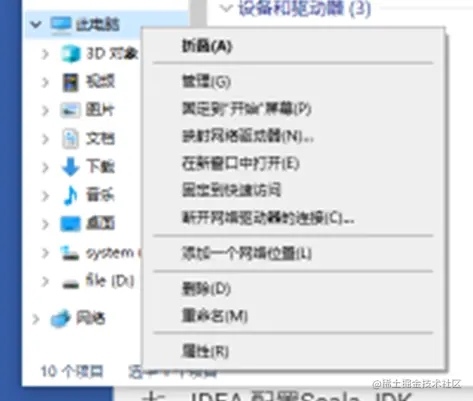

对此电脑,按右键,选属性

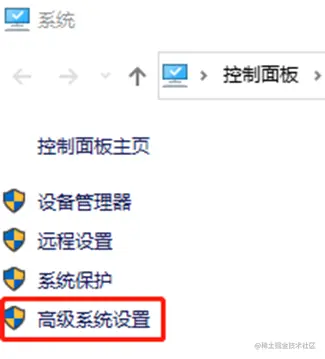

选择高级系统设置

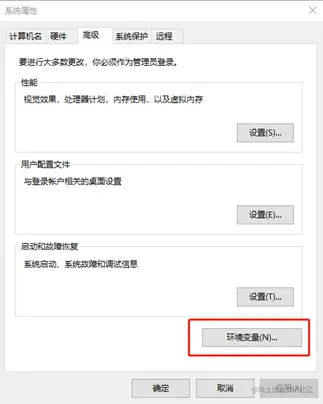

选择环境变量

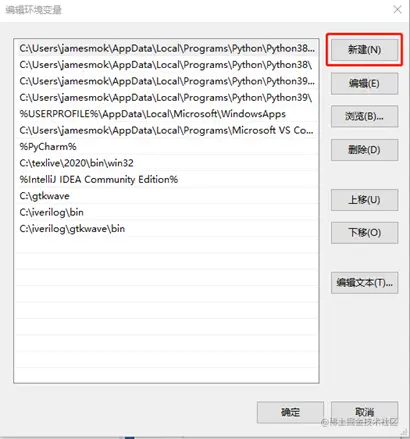

先按Path,再按编辑

按新建,再把刚才的路径贴上再按确定就可以了

重新打开cmd,输入scala -version,如果出现以下画面即环境配置成功

IDEA配置

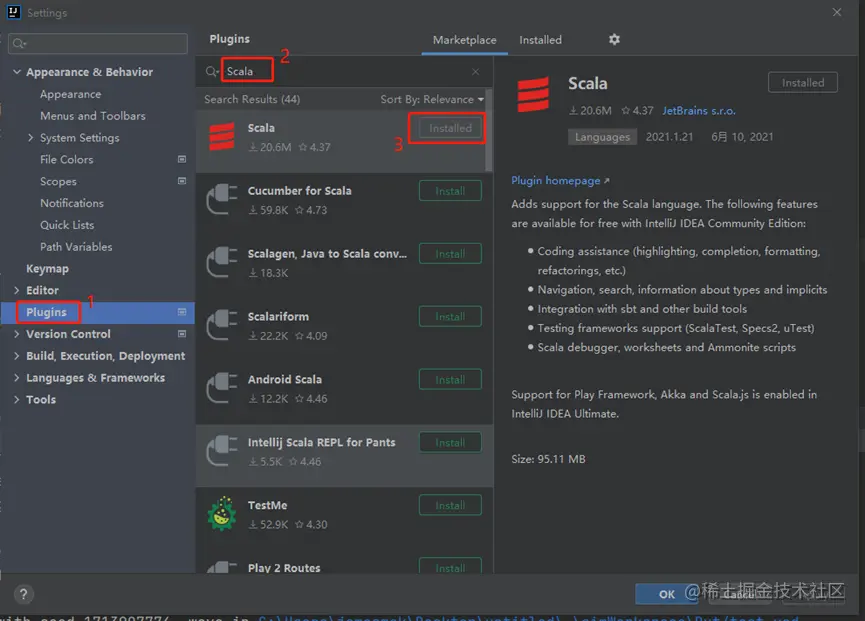

进入IDEA安装Scala插件

按File->Settings调出设置窗口,找到Plugins并搜索Scala插件

DEA 配置Scala JDK

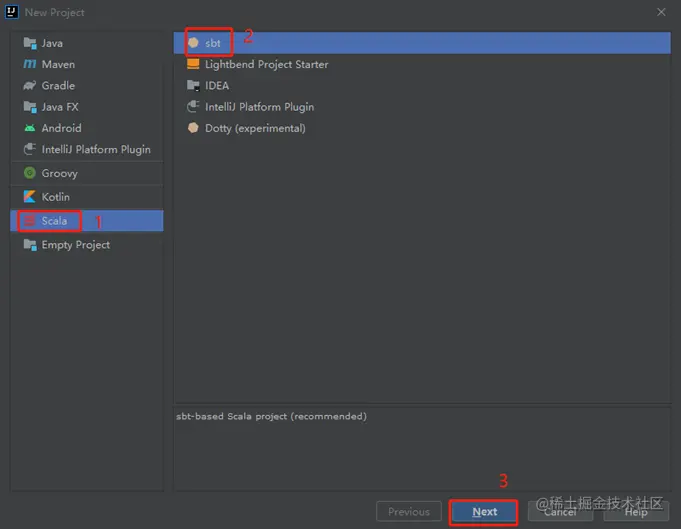

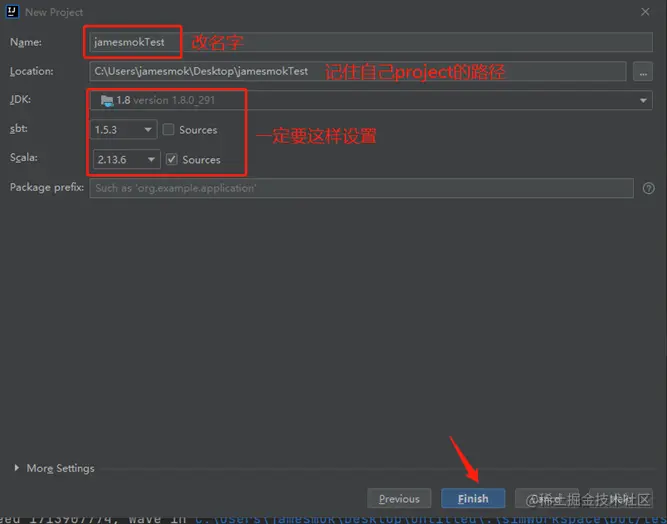

建立sbt工程文件,建立方法如下

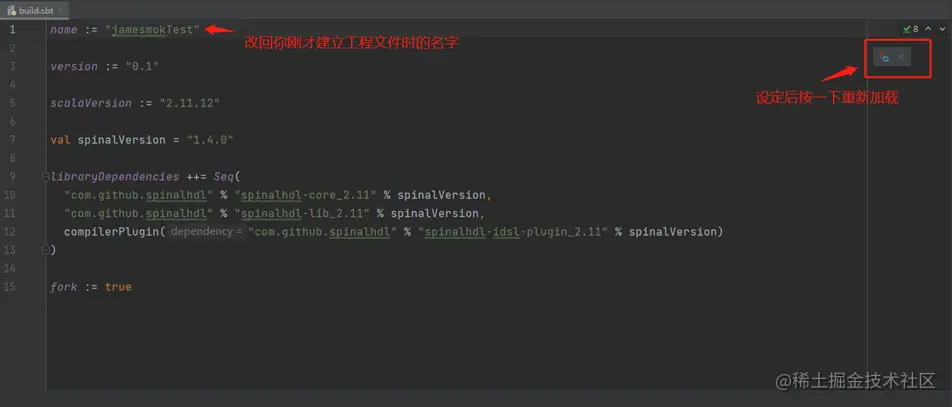

建立工程文件,设置build.sbt文件,设置如下

name := "untitled2"

version := "0.1"

scalaVersion := "2.11.12"

val spinalVersion = "1.4.0"

libraryDependencies ++= Seq(

"com.github.spinalhdl" % "spinalhdl-core_2.11" % spinalVersion,

"com.github.spinalhdl" % "spinalhdl-lib_2.11" % spinalVersion,

compilerPlugin("com.github.spinalhdl" % "spinalhdl-idsl-plugin_2.11" % spinalVersion)

)

fork := true

等待工具自动加载完成后可看到SpinalHDL已成功加载

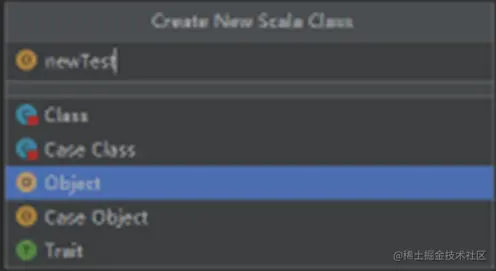

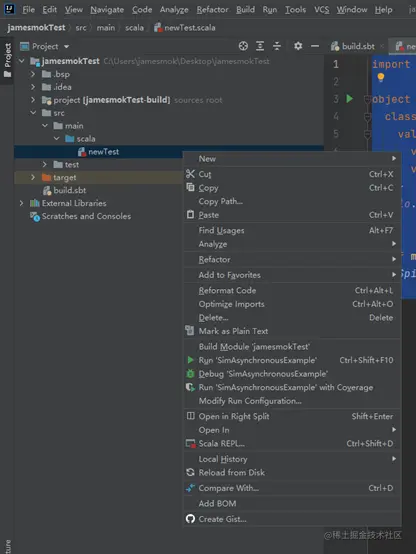

创建Scala文件

生成Verilog的例子

配置环境后,當然要運行代碼測試是否完成環境配置

//newTest.scala

import spinal.core._

object SimAsynchronousExample {

class Dut extends Component {

val io = new Bundle {

val a, b, c = in UInt (8 bits)

val result = out UInt (8 bits)

}

io.result := io.a + io.b - io.c

}

def main(args: Array[String]): Unit = {

SpinalSystemVerilog(new Dut) //* *这行的意思就是把SpinalHDL翻译成Verilog

}

}

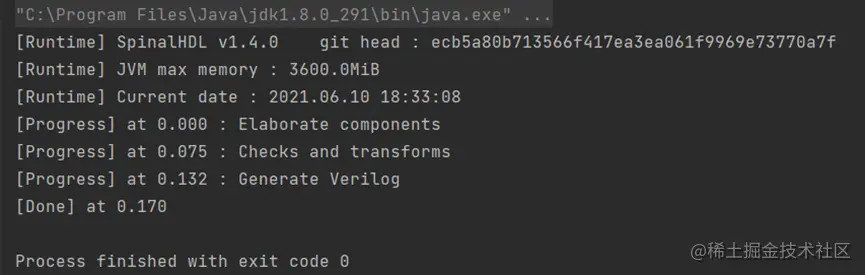

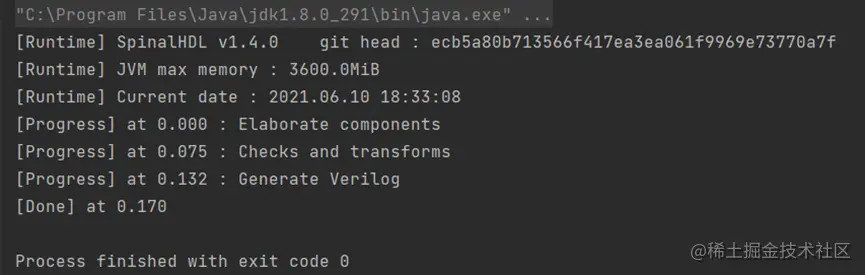

编译并运行,按Run

看见如下信息代表编译并运行成功

它会生成Verilog档案,𥚃面有刚生成的Verilog代码

SpinalHDL仿真环境

只生成Verilog代码,没有运行演示总觉得差了点什么,以下为搭建仿真环境教学。其实SpinalHDL提供了sim功能,方便用户进行仿真。

安装MSYS2

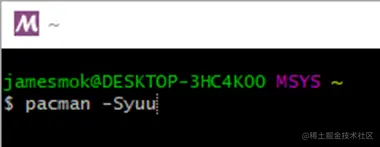

打开MSYS2,输入指令pacman -Syuu,完成后它会提示重开

重开后,输入下列指令以安装所需软件

pacman -Syuu

# Close the MSYS2 shell once you're asked to

pacman -Syuu

pacman -S --needed base-devel mingw-w64-x86_64-toolchain \

git flex\

mingw-w64-x86_64-cmake

pacman -U http://repo.msys2.org/mingw/x86_64/mingw-w64-x86_64-verilator-4.032-1-any.pkg.tar.xz

安装完成后加入 C:\msys64\usr\bin;C:\msys64\mingw64\bin 到环境变量(前面己演示过)

重开IDEA

安装Gtkwave

这是个示波器,方便观察运行结果,以下为安装方法

下载iverilog安装包,它𥚃面有gtkwave

安装后自行配置环境变量,或者在安装时勾选加入环境变量 Path:C:\\iverilog\\bin;C:\\iverilog\\gtkwave\\bin

通过一个例子进行仿真

这段代码大概意思就是随机生成100组数据进行异步加法,等下会通过gtkwave来观察运行

import spinal.sim._

import spinal.core._

import spinal.core.sim._

import scala.util.Random

object SimAsynchronousExample {

class Dut extends Component {

val io = new Bundle {

val a, b, c = in UInt (8 bits)

val result = out UInt (8 bits)

}

io.result := io.a + io.b - io.c

}

def main(args: Array[String]): Unit = {

SimConfig.withWave.compile(new Dut).doSim{ dut =>

var idx = 0

while(idx < 100){

val a, b, c = Random.nextInt(256)

dut.io.a #= a

dut.io.b #= b

dut.io.c #= c

sleep(1) // Sleep 1 simulation timestep

assert(dut.io.result.toInt == ((a + b - c) & 0xFF))

idx += 1

}

}

}

}

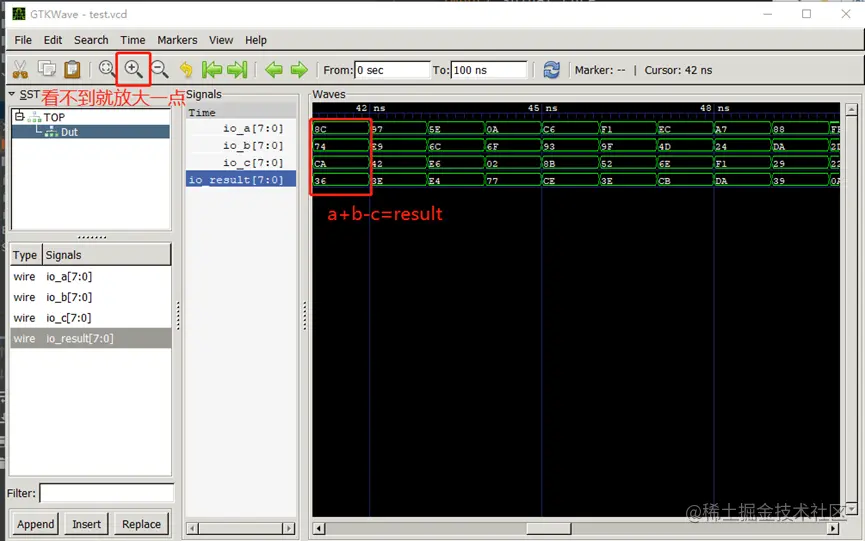

成功时会显示以下信息,然后会在workspace𥚃有vcd文件,用gtkwave打开

直接用cmd打开vcd文件,首先要移动位置,输入cd到你的vcd当前目录(dir为显示当前目录有什么文件,等同于linux的ls)

输入gtkwave 档案名.vcd 打开文件

这𥚃有100组数据,以第一组数据为例,8C+74-CA=36,不信的话按计算器算一下,通过vch文件可以更直观地观察结果

Reference

本人推介微信公众号:Spinal FPGA,这里有很多有关SpinalHDL的资讯!

SpinalHDL的官方文档:

https://spinalhdl.github.io/SpinalDoc-RTD/index.html

全平台轻量开源verilog仿真工具iverilog+GTKWave使用教程

https://zhuanlan.zhihu.com/p/95081329

在Windows 10下配置和使用Icarus Verilog (iverilog)和GTKWave

https://www.twblogs.net/a/5c9e960abd9eee73ef4b65fd

Intellij IDEA 安装Scala插件 + 创建Scala项目(Hello World!)

https://blog.csdn.net/Appleyk/article/details/82180599

idea添加scala环境_SpinalHDL——环境搭建

https://blog.csdn.net/weixin_39983404/article/details/111627298

msys2安装gcc、g++编译器

https://blog.csdn.net/Lazybones_3/article/details/88633738

如何以 MinGW 和 MSYS2 建置 C 和 C++ 開發環境

https://michaelchen.tech/windows-programming/mingw-msys/

SpinalHDL 环境搭建(1)

https://blog.csdn.net/AS7062031/article/details/110850892

SpinalHDL 开发环境 Windows 安装

https://blog.csdn.net/htgoco/article/details/113037450

用Verilator仿真Ibex的hello world

https://zhuanlan.zhihu.com/p/108624018